A taste of VHDL

1. History

For developing extremely complex ICs of hundreds of thousands of gates, VHDL, a new hardware description language, was proposed in 1981, issuing:

- Description of complex ICs

- Standardisation for sourcetext exchangeability

Version 7.2 was released for public review in August 1985, and, after some revisions and changes, VHDL was adopted as IEEE-standard 1076 in December 1987. The language was updated in 1992 with some minor improvements.

2. The meaning of the name

Like the acronym MRC, where the first letter M itself denotes an acronym, VHDL stands for VHSIC Hardware Description Language with VHSIC meaning Very High Speed Integrated Circuit, a program funded by the american Department of Defense (DoD) in the late 1970s and early 1980s. So VHDL isn't a programming-, but a hardware description language! Therefore, sourcetexts written in VHDL are refered to as design descriptions or models.

3. Designing in VHDL

VHDL is used to design and document electronic systems. It provides the textual and formal and thus executable description of a design. You can either design top-down or bottom-up by creating a behavioral and/or structural model and validating it with a simulator.

In VHDL, design activities are organized in projects. Therefore, to start working, you first must create a project. After having opened it, you'll find the work library, where the compiled components will be stored. New VHDL designs must be added explicitly to a project.

Compiling a VHDL design yields a netlist, which can be simulated and synthesized.

To avoid spending money for nothing, i.e. producing ICs with design errors, circuit behaviour must be simulated before the chip is manufactured. The later such errors are detected, the more expensive is it to remove them. At the end of this process there'll be a mask layout for ASIC production or a bitstream file to be loaded into an FPGA device. Since the 1-Chip-MSX will be implemented in such a device, we need not bother about mask layout and the things related.

VHDL offers three ways of describing hardware, which can be intermixed freely:

- Dataflow description

- Algorithmic description

- Structural description

Dataflow description is using boolean equations, while an algorithmic description looks similar to the source code of programming languages like Pascal or Ada. Algorithmic and dataflow descriptions are behavioural descriptions on different abstraction levels, in structural descriptions, components are instantiated and wired up by signals.

4. Names in VHDL

A name (identifier) in VHDL must begin with a letter, followed by letters, digits, and maybe with underscores within. VHDL is not case sensitive, so x is not distinguished from X. Within the same scope, two different objects cannot have the same name.

5. Types in VHDL

VHDL is a strongly typed language allowing some kind of errors to be detected as early as possible in the development cycle. The first value in the type's enumeration of constants is used as the simulator's default initial value for signals of that type.

6. Interfaces and architectures

To understand the important concept of separating interfaces from architectures, let us first consider schematics:

In a schematic, there are components connected by wires. The component is a named black box telling about its functionality, but hiding implementation details of its design. Each component has named wires going in and out the box, letting you just know about its interface.

Similarly, one major concept of VHDL is the separation of interface description from the description of how the design is implemented, called its architecture.

In VHDL, the resered word entity introduces a name for

the interface of a component.

The keyword architecture introduces the description of

an implementation of a certain component.

Actually, for a certain entity, more than one architecture may exist, each of them intended for realizing the same functionallity in a different way: So, one may require a high amount of chip space, but would work very fast, while another one would need less space but would be slower.

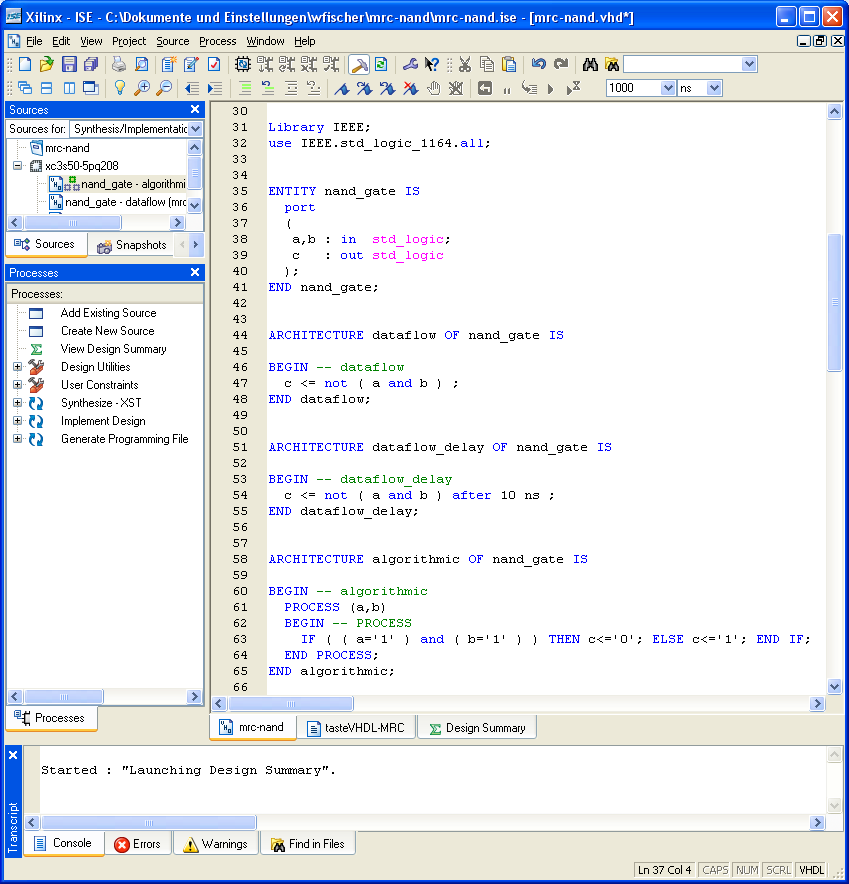

7. Description of a NAND gate in VHDL

In VHDL, comments start with the -- symbol and are at most one line.

The <= symbol denotes signal assignement.

Library IEEE;

use IEEE.std_logic_1164.all;

ENTITY nand_gate IS

port

(

a,b : in std_logic;

c : out std_logic

);

END nand_gate;

ARCHITECTURE dataflow OF nand_gate IS

BEGIN -- dataflow

c <= not ( a and b ) ;

END dataflow;

ARCHITECTURE dataflow_delay OF nand_gate IS

BEGIN -- dataflow_delay

c <= not ( a and b ) after 10 ns ;

END dataflow_delay;

ARCHITECTURE algorithmic OF nand_gate IS

BEGIN -- algorithmic

PROCESS (a,b)

BEGIN -- PROCESS

IF ( ( a='1' ) and ( b='1' ) ) THEN c<='0'; ELSE c<='1'; END IF;

END PROCESS;

END algorithmic;

7.1. Library

To open a library to access a compiled entity (component),

a library declaration must precede the entity declaration.

For the built-in libraries WORK and STD,

no library statement is required.

std.standard.all is set by default.

The use statement makes library elements directly available to the

design unit, without having to use selected names, that means compound names

separated by a dot. Its scope is limited to the design unit it precedes.

Type std_logic declared in the IEEE library is made available

through the library declaration and the use statement preceding

the declaration of the entity nand_gate.

7.2. Entity

In the port list of entity nand_gate, every port is

of type std_logic.

Note that, between colon and type designator, there are either

in or out to specify the direction of the signals.

7.3. Architecture

In VHDL, an architecture specifies the entity it belongs to.

Architecture dataflow just contains a boolean expression

assigned to the outgoing port.

Additionally, in architecture dataflow_delay,

there's a delay time of 10 nanoseconds specified in order to model

the gate's propagation delay.

For simulation, you can see the impact of changing the delay time

for some gates or components to the operation of the whole design.

For synthesis, since we use an FPGA, the propagation delay of

the CLB emulating the gate is constant and need not to be modeled.

In architecture algorithmic of entity nand_gate,

the process-statement indicates an algorithmic description.

The parenthesised list following the keyword process is called

sensitivity list.

During simulation, the process will only be executed if there's a change

in at least one of the signals of that list.

8. Simulation

The compiled components in the WORK library can be seen as templates for possibly many instances of them in the architectures of other entities. To check if the nand gate works right, it must be instantiated in a special architecture to simulate it. The declarations made there provide our gate with the required signals and stimuli values.

Library IEEE;

use IEEE.std_logic_1164.all;

ENTITY SimBox IS

END SimBox;

ARCHITECTURE test_nand OF SimBox IS

COMPONENT nand_gate

port

(

a,b : in std_logic;

c : out std_logic

);

END COMPONENT;

SIGNAL a_test, b_test, c_test : std_logic;

BEGIN -- test_nand

my_nand_gate : nand_gate

port map

(

a => a_test,

b => b_test,

c => c_test

);

a_test

<=

'0' after 0 ns,

'1' after 2 ns,

'0' after 4 ns,

'1' after 6 ns

;

b_test

<=

'0' after 0 ns,

'0' after 2 ns,

'1' after 4 ns,

'1' after 6 ns

;

END test_nand;

The entity SimBox doesn't need any input or output lines,

so the port statement is omitted.

It's architecture contains the component declaration of the nand gate.

Then, three signals are declared to be from type std_logic

to wire up the gate.

In the statement block of the architecture test_nand,

my_test_nand is instantiated to be a nand_gate

and connected to the previously declared signals via its port map.

The next two statements are to supply the signals a_test

and b_test with stimuli.

9. Configuration

As a consequence of the linguistic separation of interface and architecture, VHDL needs a mechanism to tell the compiler which architecture to take for creating the netlist. This is accomplished by configuration statements.

CONFIGURATION nand_test_dataflow OF SimBox IS

FOR test_nand

FOR my_nand_gate : nand_gate

use entity work.nand_gate(dataflow);

END FOR; -- my_nand_gate

END FOR; -- test_nand

END nand_test_dataflow;

CONFIGURATION nand_test_dataflow_delay OF SimBox IS

FOR test_nand

FOR my_nand_gate : nand_gate

use entity work.nand_gate(dataflow_delay);

END FOR; -- my_nand_gate

END FOR; -- test_nand

END nand_test_dataflow_delay;

CONFIGURATION nand_test_algorithmic OF SimBox IS

FOR test_nand

FOR my_nand_gate : nand_gate

use entity work.nand_gate(algorithmic);

END FOR; -- my_nand_gate

END FOR; -- test_nand

END nand_test_algorithmic;

This mechanism is very useful if you need to simulate a design consisting of many components, where each of them can be realized in many ways.

Imagine, you have to design a device build up of two different components, where one can be implemented in 3 and the other in 7 different ways. So, there are 21 different combinations realizing the required functionality. Maybe only 9 of them are interesting to you, because you already know that the others will be too expensive or too slow.

Wolfgang Fischer (Tanni)