Section 5 MSX-MIDI

From MSX Datapack Vol. 3

Translated by Laurens Holst

Attached files: thru.mac, thru.doc, thru.com

Chapter 1: About MSX-MIDI

With MSX-MIDI, MIDI functionality and BASIC extensions were added to MSX-MUSIC to enable it to use MIDI. Unlike MSX-MUSIC, there is no BIOS. Non-BASIC MSX-MIDI programs directly access the hardware from the I/O ports.

MSX-MIDI can be both built into the machine body, or an external cartridge. MSX MIDI is only available to MSX turbo R and later. It can not be used on MSX, MSX2 and MSX2+.

MSX-MIDI is organized as follows:

-

MIDI interface

8251 MIDI data communication IC 8253 or 8254 Baud rate generator and timer IC These ICs can be accessed through the I/O ports.

-

MSX-MIDI ROM (16K bytes)

In case it is built-in, it is placed in the same slot as the MSX-Music (slot 0-2, page 1).

In case it is an external cartridge, it is included on the cartridge. When the BASIC extensions are used, it is initialized to use external cartridge’s MSX-MIDI instead of the built-in MSX-MUSIC.

Chapter 2: Hardware

Between internal or external MSX-MIDI, the hardware configuration and access methods and such is different. What follows is a description of the MSX MIDI hardware configuration.

Additionally, regardless of whether timer IC 8253 or 8254 is used, it will henceforth be referred to as “8253”.

2.1 Block Diagram

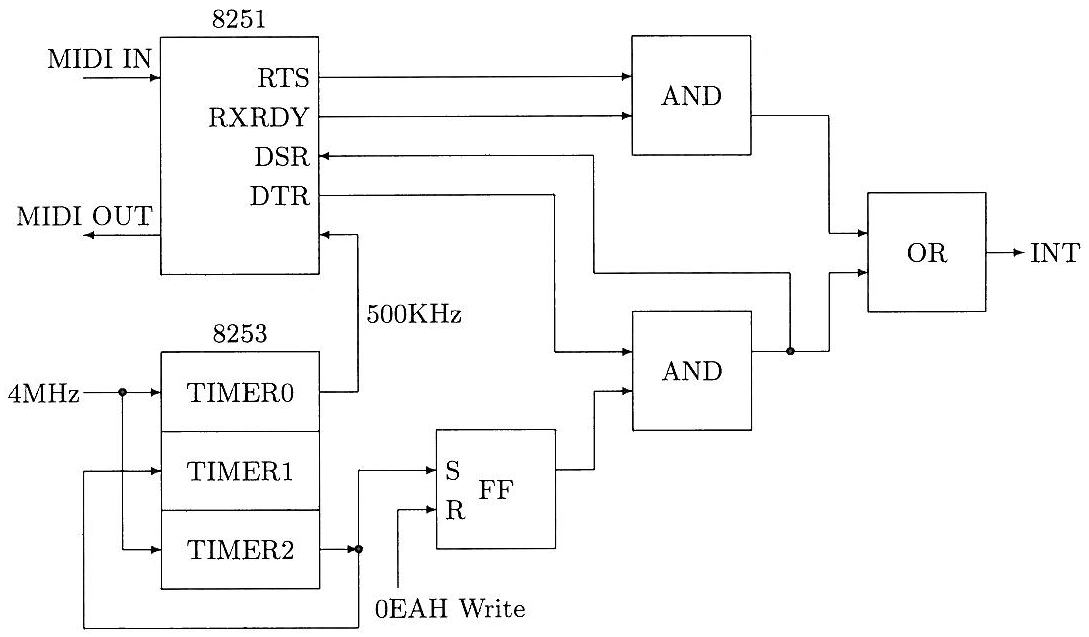

The MSX-MIDI hardware is organised as follows:

Figure 4.1 MSX-MIDI block diagram

2.2 Internal MIDI interface

The I/O ports of the built-in MSX-MIDI interface are assigned as follows:

-

8251 interface (address 0E8H, 0E9H)

b7 b6 b5 b4 b3 b2 b1 b0 0E8H (Read) RXD7 RXD6 RXD5 RXD4 RXD3 RXD2 RXD1 RXD0 (Write) TXD7 TXD6 TXD5 TXD4 TXD3 TXD2 TXD1 TXD0 RXD7-RXD0 8251 receive data TXD7-TXD0 8251 transmit data b7 b6 b5 b4 b3 b2 b1 b0 0E9H (Read) DSR BRK FE OE PE EMPT RRDY TRDY DSR 8253 timer interrupt flag (1=interrupt occurs) BRK 8251 break code detection (1=detected) FE 8251 frame error flag (1=error occurs) OE 8251 overrun error flag (1=error occurs) PE 8251 parity error flag (1=parity error occurs) EMPT 8251 transmit buffer status (1=transmit buffer empty) RRDY 8251 receive buffer status (1=data available) TRDY 8251 transmit status (1=transmission possible) 0E9H (Write) b7 b6 b5 b4 b3 b2 b1 b0 Mode S2 S1 EP PEN L2 L1 B2 B1 Command EH IR RIE ER SBRK RE TIE TEN EH Normally set to 0 IR Normally set to 0 RIE MIDI IN interrupt enable (1=enable, 0=disable) ER Error reset (1=reset error flag)

(0=no operation)SBRK Normally set to 0 RE MIDI IN receive enable (1=enable, 0=disable) TIE 8253 timer (counter #2)

interrupt enable(1=enable, 0=disable) TEN MIDI OUT transmit enable (1=enable, 0=disable) For 8251 command / mode register writes, a recovery time of at most 16 clock ticks (at 3.579545MHz) is necessary. When writing to the command / mode register continuously, please insert a wait to allow the 8251 to reinitialise.

By writing 00H, 00H, 00H, 40H to I/O port 0E9H, the 8251 is reset. It will no longer function as MIDI if an incorrect mode value is configured, so after a reset always set it to a specific value. For more information, please see the attached sample program (THRU.MAC).

-

8253 OUT2 latch pin signal (address 0EAH, 0EBH)

b7 b6 b5 b4 b3 b2 b1 b0 0EAH (Write) — — — — — — — — Reading address 0EAH is invalid Address 0EBH is an image of 0EAH The interrupt from counter #2 is released by writing any data to address 0EAH.

-

8253 Interface (address 0ECH-0EFH)

b7 b6 b5 b4 b3 b2 b1 b0 0ECH (R/W) CT07 CT06 CT05 CT04 CT03 CT02 CT01 CT00 0EDH (R/W) CT17 CT16 CT15 CT14 CT13 CT12 CT11 CT10 0EEH (R/W) CT27 CT26 CT25 CT24 CT23 CT22 CT21 CT20 0EFH (Read) — — — — — — — — (Write) SC1 SC0 RW1 RW0 M2 M1 M0 BCD CT07-CT00 Counter #0 CT17-CT10 Counter #1 CT27-CT20 Counter #2 SC1, SC0 Counter select, command select RW1, RW0 Counter read-write mode M2, M1, M0 Counter mode BCD Binary / BCD count select The function of each counter is as follows:

-

Counter #0

Is used as the 8251’s baud rate generator. A 4 MHz clock signal is input to the CLK pin. For the 8251, it must be configured to transmit a baud rate clock of 500 KHz (divided by 8). Use mode 3 (square wave divide-by-N mode).

-

Counter #1

Can be used as general-purpose counter. The output of counter #2 is input to the CLK pin.

-

Counter #2

Used as a periodic interrupt to the CPU (used by BASIC for 5 ms interval interrupts). Normally, mode 2 (divide-by-N mode) is used. OUT2 pin goes low, and through the latch circuit a CPU interrupt is generated. A 4 MHz clock is input to the CLK pin.

-

2.3 External MIDI Interface

The external MSX-MIDI interface’s I/O port address can be changed by setting a value to I/O port 0E2H.

-

MIDI interface configuration (address 0E2H, 0EAH)

b7 b6 b5 b4 b3 b2 b1 b0 0E2H (Write) EN — — — — — — E8 EN MIDI interface usage allow / deny

Initial value is 1.(0=allow, 1=deny) E8 8251 address configuration

Initial value is 1.(1=address 0E0H, 0E1H)

(0=address 0E8H, 0E9H)Set bit E8 to 0, and the external cartridge MIDI interface’s I/O ports change from 0E2H to 0EAH, becoming compatible with the internal MIDI interface. Also, the 8251’s I/O address becomes 0E8H and 0E9H.

Set bit E8 to 1 and the 8251 interface addresses will be 0E0H and 0E1H, and access to the cartridge’s I/O ports 0ECH-0EFH will be prohibited. Additionally, the 8253’s timer interrupt is also inhibited.

-

8251 interface (address 0E0H, 0E1H)

(in case E8 bit is 1)

b7 b6 b5 b4 b3 b2 b1 b0 0E0H (Read) RXD7 RXD6 RXD5 RXD4 RXD3 RXD2 RXD1 RXD0 (Write) TXD7 TXD6 TXD5 TXD4 TXD3 TXD2 TXD1 TXD0 RXD7-RXD0 8251 receive data TXD7-TXD0 8251 transmit data b7 b6 b5 b4 b3 b2 b1 b0 0E1H (Read) DSR BRK FE OE PE EMPT RRDY TRDY DSR 8253 timer interrupt flag (1=interrupt occurs) BRK 8251 break code detection (1=detected) FE 8251 frame error flag (1=error occurs) OE 8251 overrun error flag (1=error occurs) PE 8251 parity error flag (1=parity error occurs) EMPT 8251 transmit buffer status (1=transmit buffer empty) RRDY 8251 receive buffer status (1=data available) TRDY 8251 transmit status (1=transmission possible) 0E1H (Write) b7 b6 b5 b4 b3 b2 b1 b0 Mode S2 S1 EP PEN L2 L1 B2 B1 Command EH IR RIE ER SBRK RE TIE TEN EH Normally set to 0 IR Normally set to 0 RIE MIDI IN interrupt enable (1=enable, 0=disable) ER Error reset (1=reset error flag)

(0=no operation)SBRK Normally set to 0 RE MIDI IN receive enable (1=enable, 0=disable) TIE 8253 timer (counter #2)

interrupt enable(1=enable, 0=disable) TEN MIDI OUT transmit enable (1=enable, 0=disable)

2.4 Method to distinguish internal from external type

In case bit 0 of MAIN ROM address 002EH is 1, the MSX-MIDI is internal.

In models whose MAIN ROM version number (002DH) is 03H or more, the features of the MSX-MIDI can be used with an external cartridge.

In the internal type and the external type, the hook is different. This distinction is important in order to create an application. For hooks, please see 3.2 “Hooks” and chapter 4 “Application development”.

To make the distinction between internal type and external type, examine the string starting at MSX MIDI ROM address 4018H.

| Address | Internal | External |

|---|---|---|

| 4018H | 41H (A) | ??H (?) |

| 4019H | 50H (P) | ??H (?) |

| 401AH | 52H (R) | ??H (?) |

| 401BH | 4CH (L) | ??H (?) |

| 401CH | 4FH (O) | 4DH (M) |

| 401DH | 50H (P) | 49H (I) |

| 401EH | 4CH (L) | 44H (D) |

| 401FH | 4CH (L) | 49H (I) |

In external cartridges, the 4 unspecified bytes at 4018H are different for each manufacturer. The data at 401CH consists of “MIDI”.

2.5 Method to detect presence of MIDI interface

The presence or absence of the MIDI interface can be determined in the following manner:

-

In case MAIN ROM address 002EH bit 0 is 1, the MIDI interface is internal.

-

In case the MAIN ROM version number (002DH) is 03H or more, look for a slot which contains the following in 401CH-401FH:

DB "MIDI"

If it exists, the external cartridge is inserted.

-

When the above cases do not apply, since there is no MIDI interface, the MIDI function can not be used.

-

In case the ROM version number is 02H or less, the MIDI interface can not be used.

Chapter 3: Interrupts

3.1 Interrupts in BASIC

1/60 sec (NTSC) or 1/50 sec (PAL) interrupts have been used for the MSX-MUSIC, but in the MSX-MIDI BASIC extensions 5 ms interrupts from the 8253 are used.

3.2 Hooks

The MSX turbo R built-in MSX-MIDI’s hooks are as follows:

| Address | Name | Former name | Content |

|---|---|---|---|

| 0FF75H | H.MDIN | H.OKNORM | MIDI IN interrupt |

| 0FF93H | H.MDTM | H.FRQINT | 8253 timer interrupt |

In case of external cartridge, because these hooks can not be used, please use H.KEYI. Usage details are described in chapter 4 “Application Development”.

| Address | Name |

|---|---|

| 0FD9AH | H.KEYI |

Chapter 4: Application Development

4.1 Notes regarding application development

When creating an application program that supports MSX-MIDI, please note the following points:

-

The hooks are different depending on whether MIDI is built-in or external. When setting up a hook, please check if the type is internal or external.

-

When enabling interrupts, such as after MIDI interface initialization, because there is a possibility that the interrupt flag has already been set, the interrupt flag must be reset.

Interrupt flags are as follows:

Table 4.4 MIDI interface interrupt flags Interrupt type Interrupt distinction Interrupt clear method Timer Bit 7 (DSR) of 0E9H or 0E1H Write any value to 0EAH MIDI IN Bit 0 (RRDY) of 0E9H or 0E1H Read 0E8H with IN instruction -

With the external cartridge, other interrupts besides MIDI IN and 8253 timer also come from H.KEYI. Therefore, the interrupt handling routine must detect what kind of interrupt the current interrupt is.

Whether or not it is a MIDI IN interrupt can be checked in bit 1 of I/O port address 0E9H.

Whether or not it is an interrupt from the 8253 timer can be checked in bit 7 of I/O port address 0E9H.

-

At the shortest, the MIDI IN receive interrupt occurs at 320 µs intervals. When calling an interrupt handling routine from the hook with the RST 30H instruction, the inter-slot call takes time to process and will not complete in time for 320 µs interval reception.

For that reason, set up interrupts as follows:

-

Place the interrupt handling routine in page 3

-

Jump from the hook to the interrupt handling routine with the JP instruction

-

4.2 Sample program

For MIDI interface and hook set up / tear down, please refer to the included sample program (THRU.MAC).

Chapter 5: BASIC Extensions

TODO

Grauw